系统:PC

日期:2021-04-24

类别:行业软件

版本:v9.0

Quartusii9.0是一款用处非常大的编程软件,用户深爱它的高效性和完美的操作性,可以方便地实现各种DSP应用系统,支持集成系统设计、嵌入式软件开发等多项功能于一体,是每个开发设计程序员的首要之选。

1、Quartusii9.0可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

2、芯片(电路)平面布局连线编辑;

3、LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

4、功能强大的逻辑综合工具;

5、完备的电路功能仿真与时序逻辑仿真工具;定时/时序分析与关键路径延时分析;可使用SignalTapII逻辑分析工具进行嵌入式的逻辑分析;

6、Quartusii9.0支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

7、使用组合编译方式可一次完成整体设计流程;

8、自动定位编译错误;

9、高效的期间编程与验证工具;

10、可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;

11、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

1、首先我们打开电脑,登录好账号之后进入桌面,双击安装好的Quartus II 软件,进入本软件的程序界面

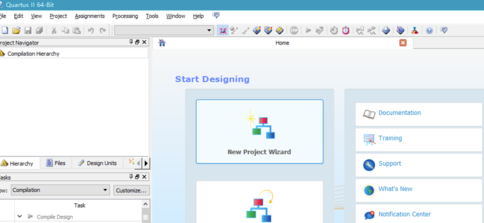

2、稍等片刻,等待所有模块加载完毕后,即可来到欢迎界面,我们点击New Project Wizard,进入工程向导

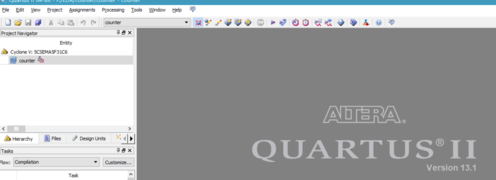

3、首先选择工程文件夹的路径,并设定好相应的仿真设备型号,最后选择我们使用的硬件描述语言如VHDL即可创建好一个空白的工程

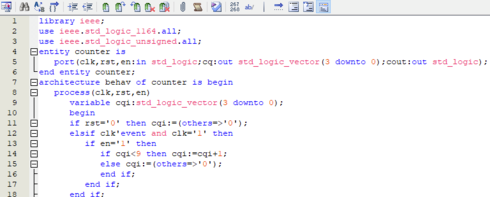

4、可以使用两种方式来设定我们的硬件线路连接,第一种是使用原理图输入法,第二种是使用硬件描述语言,我们使用第二种,此处为十进制计数器的VHDL描述

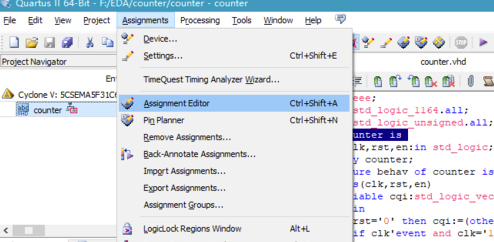

5、确认代码输入无误后,点击进行一次全编译,然后进行管脚分配的操作,点击菜单栏中的分配-分配编辑器

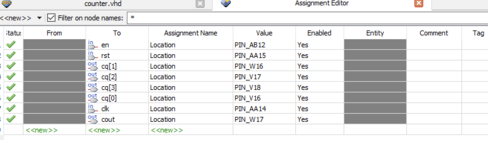

6、根据我们需要的输入变量和输出变量,根据FPGA的端口表,分别分配以对应的location,完成后再点击一次全编译,即可使用编程器将程序下载到FPGA中

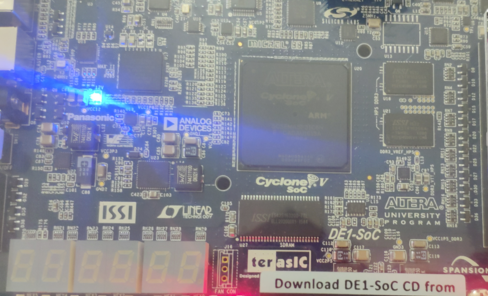

7、稍等片刻,我们的程序已经被烧录到FPGA中了,此时可以看到已经成功地将计数器的程序下栽进去了,表明管脚分配已经成功

1、在本站下载Quartusii9.0安装包

2、使用压缩软件进行解压(推荐使用winrar)

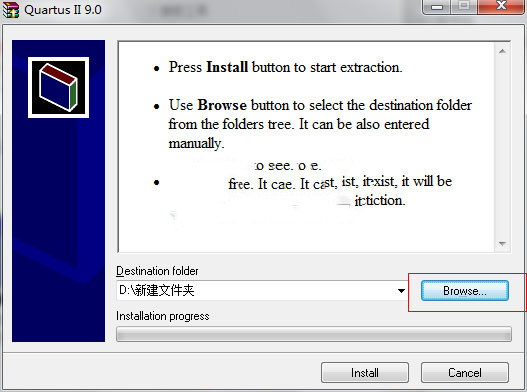

3、点击exe文件开始安装

4、选择安装目录,文件程序较大,建议安装在空间较大的D盘

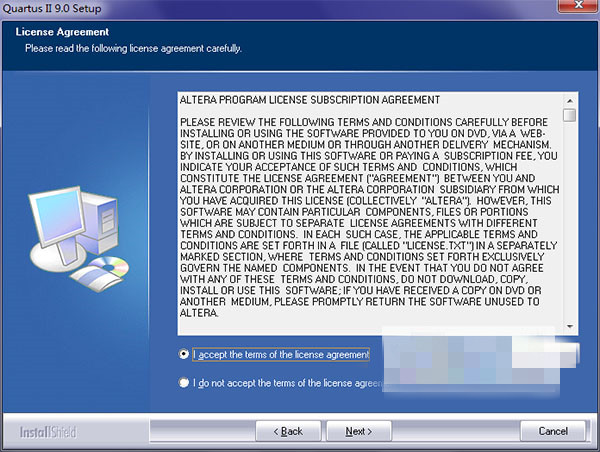

5、这里点击next-I accept

6、到这等待1到2分钟,完成主程序的安装

热门推荐

相关应用

实时热词

评分及评论

帮我了很大忙,感谢这个网站

找到了一款不错的

不仅软件很给力,教程也给力,十分需要

真心好用,很满意。

好用好用好用,重要的话说三遍。

点击星星用来评分